# User's Manual

Industrial PC-based Automation

# EmCORE-v611

3.5" Embedded Board with VIA Eden CPU onboard 128 MB SDRAM, LCD / CRT SVGA, Fast Ethernet, 3D Audio, GPIO, Two Serial Ports & DiskOnChip Socket

#### Copyright © 2002

#### All Rights Reserved.

Manual edition: 1.0 November 2002

The information in this document is subject to change without prior notice in order to improve the reliability, design and function. It does not represent a commitment on the part of the manufacturer.

Under no circumstances will the manufacturer be liable for any direct, indirect, special, incidental, or consequen-tial damages arising from the use or inability to use the product or documentation, even if advised of the possibility of such damages.

This document contains proprietary information protected by copyright. All rights are reserved. No part of this manual may be reproduced by any mechanical, electronic, or other means in any form without prior written permission of the manufacturer.

#### **Trademarks**

PC is a registered trademark of International Business Machines Corporation. Intel is a registered trademark of Intel Corporation. AWARD is a registered trademark of Award Software International, Inc. DiskOnChip®2000 and TrueFFS are registered trademarks of M-Systems Inc.. Other product names mentioned herein are used for identification purposes only and may be trademarks and/or registered trademarks of their respective companies.

Part number: 4011061100100

# **Table of Contents**

| 2        |

|----------|

| 4        |

| 5        |

| 6        |

| 7        |

| 9        |

| 9        |

| 10       |

| 10       |

| 10<br>11 |

| 12       |

| 13       |

| 13       |

| 14       |

| 14       |

| 14       |

| 15       |

| 16       |

| 16       |

| 17       |

| 17       |

| 17       |

| 18       |

| 19       |

| 19<br>20 |

|          |

| Flat Panel Connector                          | 21 |

|-----------------------------------------------|----|

| Peripheral Ports                              | 23 |

| Parallel Port (LPT1)                          | 23 |

| Dual USB Port (USB1,2)                        |    |

| IrDA (SIR)                                    |    |

| CRT SVGA (VGA)                                |    |

| PS/2 Keyboard & Mouse(KBM)                    |    |

| Onboard Serial Ports (COM1~2)                 |    |

| Audio Interface Port (AUDIO)                  |    |

| CDROM audio interface (CDIN)                  | 26 |

| 16-bit General Purpose I/O (DIO)              | 26 |

| Switches and Indicators                       | 27 |

| System Resources                              | 28 |

| AWARD BIOS Setup                              |    |

| Setup Items                                   |    |

| Standard CMOS Setup                           |    |

| IDE Harddisk Setup (submenu)                  |    |

| BIOS Features Setup                           |    |

| Chipset Features Setup                        |    |

| Integrated Peripherals Power Management Setup |    |

| PnP/PCI Configuration                         |    |

| PC Health Status                              |    |

| Frequence / Voltage Control                   |    |

| POST Codes                                    | 53 |

|                                               |    |

| Howto: Flash the BIOS                         | 60 |

|                                               |    |

| What if things go wrong                       | 61 |

| Warranty                                      |    |

#### Introduction

This SBC is based on VIA Embedded System Platform which combines PC-66/100/133MHz FSB, UltraDMA/100 IDE technologies and rich 4xAGP 2D/3D graphics capabilities in a single package. Its onboard Dual 10Base-T/100Base-TX Fast Ethernet, CRT /LCD display controller, with VGA / TTL / LVDS Interfaces add communication and multimedia features to its powerfull function.

The new VIA Eden Embedded System Platform will spur the further development of the emerging new generation of quiet running, low profile small factor designs that are being adopted for a myriad of connected information and entertainment systems - ranging from home entertainment devices such as Set Top Boxes, Game Consoles, Personal Video Recorders and Broadband Gateways to commercial applications such as Thin Clients, LCD Web Based Terminals. POS Terminals and Network Attached Servers.

These new designs not only leverage the fundamental strengths of the x86 platform - namely, its software resources, its Internet compatibility, its rapid product innovation cycles, its massive economies of scale, and its open architecture. They also extend the capabilities of the PC and the Internet by allowing people to connect to information and entertainment in an easier, more convenient, and more affordable way.

This board with the new generation of information and entertainment systems is already changing the way that people consume and interact with digital content. It will allow them to view it on a TV or LCD screen, listen to it on their audio system speakers, store it on a server or Personal Video Recorder so that it can be accessed at a later date, manipulate it on a home media PC, share it with their family over the home network, or send it to their freinds and relatives over the internet.

With its ultra low power, rich levels of integration, advanced multimedia capabilities and communication features, this board is an exciting opportunity for System Integrators and OEMs to develop new generation products that meet the desires and aspirations of the 21th century consumers.

# **Specifications**

#### **General Specifications**

- CPU: VIA Ultra Low Power Embedded Eden processor (400 ~800 MHz) with FSB 66/100/133 MHz EBGA package.

- Chipset: VIA VT8606 TwisterT with Integrated Savage4 AGP 4X Graphics core and VT82C686B Super "South Bridge"

- BIOS: AWARD® Flash BIOS

- Green Function: power saving supported in BIOS. DOZE / STANDBY / SUSPEND modes, ACPI & APM

- L1 Cache: Integrated on CPU (128KB)

- L2 Cache : Integrated on CPU (64 KB)

- DRAM Memory: Onboard 128 (256MB option) SDRAM, and up to 512MB of SDRAM on SODIMM (Total of 768MB Memory)

- Enhanced IDE with UltraDMA: supports 1 port and up to 2 ATAPI devices, Ultra DMA transfer 33 MB/sec. One 44-pin (2.0 pitch) box header.

- Watchdog Timer: 127-level timer generates RESET or NMI when your application loses control over the system.

- Real-time Clock: built-in chipset with lithium battery backup. CMOS data backup of BIOS setup and BIOS default.

### High Speed Multi I/O

- Chipset: VIA VT82C686B

- Serial Ports: One high speed RS-232C ports (COM1). One high speed RS-232C/422/485 port COM2 (jumper selectable). Both with 16C550 compatible UART and 16 byte FIFO.

- USB: Two onboard USB ver 1.1 ports

- · SIR Interface : onboard IrDA TX/RX port

- Floppy Disk Drive Interface: 2 floppy disk drives, 3½" (720 KB, 1.44 MB or 2.88 MB).

- · Bi-directional Parallel Port : SPP, EPP and ECP mode.

- Keyboard and Mouse Connectors: 10pin mini header for AT keyboard and PS2 mouse

- Audio Chipset: VIA VT82C686B, AC97 2.0 compliant, Multistream Direct Sound and Direct Sound 3D acceleration. (Line-in, CD Audio in, MIC in, Speaker out)

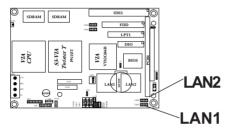

#### **Network Interface Controller**

- Chipset: 2 x Realtek 8139C, 10/100 Mbps (EmCORE-v611VL2/R Series)

- · Connector: Two 10 pin onboard header

#### **Display Controller**

- Chipset: 4x AGP S3 Savage4 3D and S3 Savage 2000 2D engines integrated in VT8606 supports up to 32MB of Shared system memory

- Display Type: CRT (VGA, SVGA, XGA, SXGA) and LCD Type with TTL & LVDS interface

- · Connectors: 16 pin onboard header

- Resolution: Single Channel of LVDS / 36-bit of TTL; all resolutions are supported up to 1280x1024.

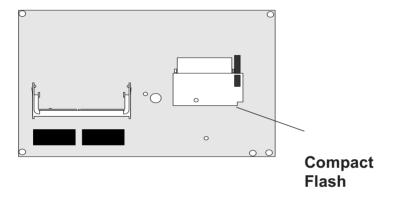

#### Flash Disk

- Compact Flash Card (CFC)

- Compact Flash Socket : supports Type I/II CFC

- Capacity: up to 512MB CFC

#### **Environmental and Power**

- Power Requirements: +5 V @ 1.8 A (typical), +12 V @ 0.13A (typical); (Low Power Embedded 667MHz and 128MB SDRAM)

- System Monitoring and Alarm : CPU and System temperature, system voltage and cooling fan RPM.

- Board Dimensions : 145mm x 102mm

- · Board Weight: 0.18kg

- Operating Temperature : 0 to 60°C (32 to 140°F)

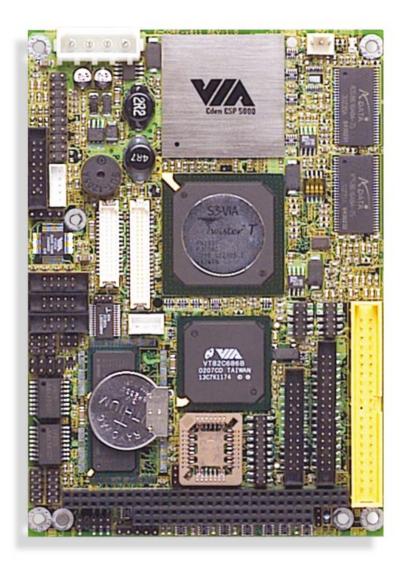

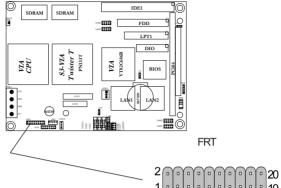

# **Board Image**

# Warning

Single Board Computers and their components contain very delicate Integrated Circuits (IC). To protect the Single Board Computer and its components against damage from static electricity, you should always follow the following precautions when handling it:

- Disconnect your Single Board Computer from the power source when you want to work on the inside

- Hold the board by the edges and try not to touch the IC chips, leads or circuitry

- B. Use a grounded wrist strap when handling computer components.

- Place components on a grounded antistatic pad or on the bag that came with the Single Board Computer, whenever components are separated from the system

#### **Ordering Codes**

EmCORE-v611VL2R/E533 3.5" form factor Embedded VIA Eden 533MHz Single Board Computer with 128MB SDRAM, CRT SVGA, Dual Fast Ethernet, AC97 3D Audio, PC/104 and Compact Flash Socket

EmCORE-v611VL2R/E667 3.5" form factor Embedded VIA Eden 667MHz Single Board Computer with 128MB SDRAM, CRT SVGA, Dual Fast Ethernet, AC97 3D Audio, PC/104 and Compact Flash Socket (optional)

EmCORE-v611VL2R/E800 The same as above with VIA Eden 800MHz CPU (optional)

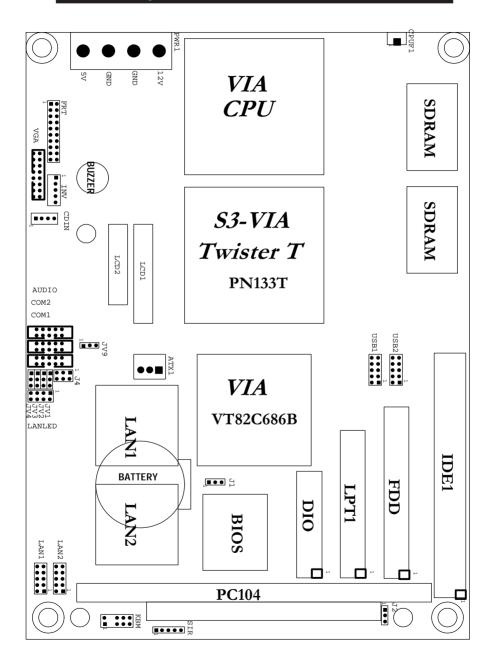

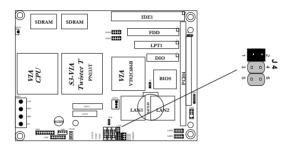

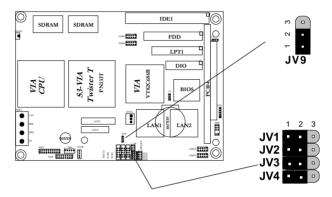

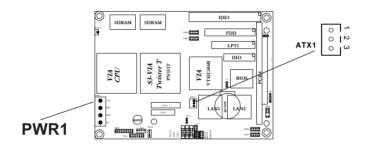

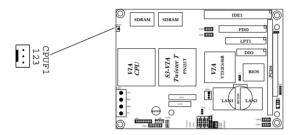

# **Board Layout Front**

# Jumper/Connector Quick Reference

Jumpers

| dampord |                              |

|---------|------------------------------|

| Lable   | Function                     |

| J1      | Clear CMOS                   |

| J2      | Watchdog Output              |

| J4      | RS-232 / 422 / 485 Selection |

| JV1~4   | RS-232 Mode Selected         |

| JV9     | LCD Voltage slected          |

# Jumper/Connector Quick Reference

| Connectors |                                     |

|------------|-------------------------------------|

| Lable      | Function                            |

| ATX1       | ATX Feature Connectorr              |

| COM1       | Serial Port: COM1                   |

| COM2       | Serial Port: COM2                   |

| CPUF1      | CPU FAN1 Connector                  |

| ESMI       | External SMI                        |

| ESPK       | External Speaker                    |

| FDD        | Floppy Disk Driver Connector        |

| HLED       | HDD LED Connector                   |

| IDE1       | Primary IDE Connector               |

| KBM(PS2)   | PS/2 Keyboard & Mouse               |

| LAN1       | 10/100M LAN1 Connector              |

| LAN2       | 10/100M LAN2 Connector              |

| LANLED     | LED Singal for LANs                 |

| LPT1       | Parallel Port                       |

| PLKL       | Power LED                           |

| PSON       | ATX Soft Power Switch               |

| DIO        | 16-bit GPIO                         |

| CFA1       | Compact Flash Disk                  |

| PC104      | ISA PC-104 Interface                |

| LCD1       | LCD Connector for TTL (under 24bit) |

| LCD2       | LCD Connector for LVDS              |

| INV        | LCD Invertor connector              |

| CDIN       | CDROM Audio Interface               |

| AUDIO      | Audio Interface Port                |

| SODIM1     | SODIMM Socket                       |

| SIR        | Infrared (IR) Connector             |

| RES        | Reset Connector                     |

| USB1       | USB Port 0,1                        |

| USB2       | USB Port 2,3                        |

| VGA        | CRT SVGA Connector                  |

| PWR1       | Power Connector                     |

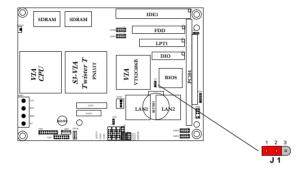

# **CMOS Jumper Settings**

CMOS Setup (J1)

Type: J1: onboard 3-pin header

CMOS Setup (J1)

| Keep CMOS       | 1-2 | ON |

|-----------------|-----|----|

| Clear CMOS      | 2-3 | ON |

| default setting |     |    |

J1

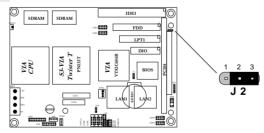

# Watchdog Timer

Watchdog Output (J2)

The onboard watchdog timer can be disable by jumper setting or enable for either reboot by system RESET or invoking an NMI (Non-Maskable Interrupt)

Even if enabled by jumper setting upon boot the watchdog timer is always inactive. To initialize or refresh the watchdog timer writing of port 444H is sufficient. To disable the watchdog time read port 44H.

| Status                            | Action         |

|-----------------------------------|----------------|

| Enable/refresh the Watchdog Timer | I/O Write 444H |

| Disable the Watchdog Timer.       | I/O Read 044H  |

After the watchdog timer has been initialized by reading port 444H, it has to be strobed at preconfigured intervals to keep it from issuing a RESET or NMI.

The watchdog timer timeout intervals are set by software programming.

### **Mode Setting**

| Watchdog Mode                             | J2   |

|-------------------------------------------|------|

| Enabled for Active NMI(I/O Channel Check) | 1-2  |

| Enabled for System Reset                  | 2-3  |

| Disable Watchdog Timer                    | None |

| defeath a title a                         |      |

#### default setting

#### **Timeout Values**

Timout values are programmed. The watchdog timer supports 127 steps. use the table on the next page to find the hexidecimal value that needs to be passed on to get the correct timer interval. Look subsequently at the program example how to pass the value to the watchdog timer.

# **Timeout Table**

| Level | Value | Seconds | Level | Value | Seconds | Level | Value | Seconds |

|-------|-------|---------|-------|-------|---------|-------|-------|---------|

| 1     | 7Fh   | 1       | 2     | 7Eh   | 2       | 3     | 7Dh   | 3       |

| 4     | 7Ch   | 4       | 5     | 7Bh   | 5       | 6     | 7Ah   | 6       |

| 7     | 79h   | 7       | 8     | 78h   | 8       | 9     | 77h   | 9       |

| 10    | 76h   | 10      | 11    | 75h   | 11      | 12    | 74h   | 12      |

| 13    | 73h   | 13      | 14    | 72h   | 14      | 15    | 71h   | 15      |

| 16    | 70h   | 16      | 17    | 6Fh   | 17      | 18    | 6Eh   | 18      |

| 19    | 6Dh   | 19      | 20    | 6Ch   | 20      | 21    | 6Bh   | 21      |

| 22    | 6Ah   | 22      | 23    | 69h   | 23      | 24    | 68h   | 24      |

| 25    | 67h   | 25      | 26    | 66h   | 26      | 27    | 65h   | 27      |

| 28    | 64h   | 28      | 29    | 63h   | 29      | 30    | 62h   | 30      |

| 31    | 61h   | 31      | 32    | 60h   | 32      | 33    | 5Fh   | 33      |

| 34    | 5Eh   | 34      | 35    | 5Dh   | 35      | 36    | 5Ch   | 36      |

| 37    | 5Bh   | 37      | 38    | 5Ah   | 38      | 39    | 59h   | 39      |

| 40    | 58h   | 40      | 41    | 57h   | 41      | 42    | 56h   | 42      |

| 43    | 55h   | 43      | 44    | 54h   | 44      | 45    | 53h   | 45      |

| 46    | 52h   | 46      | 47    | 51h   | 47      | 48    | 50h   | 48      |

| 49    | 4Fh   | 49      | 50    | 4Eh   | 50      | 51    | 4Dh   | 51      |

| 52    | 4Ch   | 52      | 53    | 4Bh   | 53      | 54    | 4Ah   | 54      |

| 55    | 49h   | 55      | 56    | 48h   | 56      | 57    | 47h   | 57      |

| 58    | 46h   | 58      | 59    | 45h   | 59      | 60    | 44h   | 60      |

| 61    | 43h   | 61      | 62    | 42h   | 62      | 63    | 41h   | 63      |

| 64    | 40h   | 64      | 65    | 3Fh   | 65      | 66    | 3Eh   | 66      |

| 67    | 3Dh   | 67      | 68    | 3Ch   | 68      | 69    | 3Bh   | 69      |

| 70    | 3Ah   | 70      | 71    | 39h   | 71      | 72    | 38h   | 72      |

| 73    | 37h   | 73      | 74    | 36h   | 74      | 75    | 35h   | 75      |

| 76    | 34h   | 76      | 77    | 33h   | 77      | 78    | 32h   | 78      |

| 79    | 31h   | 79      | 80    | 30h   | 80      | 81    | 2Fh   | 81      |

| 82    | 2Eh   | 82      | 83    | 2Dh   | 83      | 84    | 2Ch   | 84      |

| 85    | 2Bh   | 85      | 86    | 2Ah   | 86      | 87    | 29h   | 87      |

| 88    | 28h   | 88      | 89    | 27h   | 89      | 90    | 26h   | 90      |

| 91    | 25h   | 91      | 92    | 24h   | 92      | 93    | 23h   | 93      |

| 94    | 22h   | 94      | 95    | 21h   | 95      | 96    | 20h   | 96      |

| 97    | 1Fh   | 97      | 98    | 1Eh   | 98      | 99    | 1Dh   | 99      |

| 100   | 1Ch   | 100     | 101   | 1Bh   | 101     | 102   | 1Ah   | 102     |

| 103   | 19h   | 103     | 104   | 18h   | 104     | 105   | 17h   | 105     |

| 106   | 16h   | 106     | 107   | 15h   | 107     | 108   | 14h   | 108     |

| 109   | 13h   | 109     | 110   | 12h   | 110     | 111   | 11h   | 111     |

| 112   | 10h   | 112     | 113   | 0Fh   | 113     | 114   | 0Eh   | 114     |

| 115   | 0Dh   | 115     | 116   | 0Ch   | 116     | 117   | 0Bh   | 117     |

| 118   | 0Ah   | 118     | 119   | 09h   | 119     | 120   | 08h   | 120     |

| 121   | 07h   | 121     | 122   | 06h   | 122     | 123   | 05h   | 123     |

|       |       |         |       |       |         | -     |       | -       |

|       |       |         |       |       |         |       |       |         |

| 124 | 04h | 124 | 125 | 03h | 125 | 126 | 02h | 126 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 127 | 01h | 127 |     |     |     |     |     |     |

#### **Programming Example**

The following program is an examples of how to enable, disable and refresh the Watchdog timer:

WDT\_EN\_RF equ 444H

WDT\_DIS equ 044h

WT Enable push AX ; Save AX,DX

push DX

$\begin{array}{lll} \text{mov DX,WDT\_EN\_RF} & ; \text{ Enable Timer} \\ \text{mov AX,INTERVAL} \; ; \text{ Set Timeout Value} \end{array}$

out DX,AX

pop DX ; Restore DX,AX

pop AX ret

WT\_Refresh push AX ; Save AX,DX

push DX

mov DX,WDT\_EN\_RF ; Refresh Timer

mov AX,INTERVAL; Set Timout Value

out DX,AX

pop DX : Restore DX.AX

pop AX ret

WT Disable push AX ; Save AX,DX

push DX

mov DX,WDT DIS ; Disable Timer

in AX,DX

pop DX ; Restore DX,AX

pop AX ret

WT\_Disable push AX ; save AX,DX

push DX

mov DX,WDT DIS ; Disable Timer

in AX,DX

pop DX : restore DX.AX

pop AX ret

# Serial Port Selection (RS232C/422/485)

RS-232C/422/485 Mode select (J4)

#### RS-232C/422/485 Mode on COM2

The onboard COM2 port can be configured to operate in RS-422 or RS-485 modes. RS-422 modes differ in the way RX/TX is being handled. Jumper J4 switches between RS-232 or RS-422/485 mode. When J4 is set to RS-422 or 485 mode, there will be only +12V output left while J4 is set. All of the RS-232/422/485 modes are available on COM2.

#### COM2

| Pin Defined: | RS232 | RS422 | RS485 |  |

|--------------|-------|-------|-------|--|

| Pin1 :       | DCD   | Tx+   | RTx+  |  |

| Pin2 :       | RXD   | Tx-   | RTx-  |  |

| Pin8:        | CTS   | Rx+   | Х     |  |

| Pin9:        | RI    | Rx-   | Х     |  |

|              |       |       |       |  |

| J4 Selection | 1-2   | 3-4   | 5-6   |

|--------------|-------|-------|-------|

| RS-232       | Close | Open  | Open  |

| RS-422       | Open  | Close | Open  |

| RS-485       | Open  | Open  | Close |

default setting

# Voltage select

#### LCD Voltage Select (JV9)

JV1 LCD Voltage 1-2 -> 3.3 V 2-3 -> 5 V

#### RS-232c Standard and POS Modes (JV1~JV4)

All onboard COM ports can be configured to operate in standard RS-232c mode or in POS (Point-of-Sale) RS-232c mode. POS devices normally need an additional power supply signal (5V or 12V) to be able to power the device (LCD, cash drawer or printer) without additional wiring.

There are three seperate POS modes:

- RS-232 with 5V on pin 1

- RS-232 with 12V on pin 9

- RS-232 with 5V on pin 1 and 12V on pin 9

| COM1 RS-232 Mode                    | JV1        | JV2            |  |

|-------------------------------------|------------|----------------|--|

| Standard                            | 1-2        | 1-2            |  |

| POS: 12 V on pin 9                  | 2-3        | 1-2            |  |

| POS: 5 V on pin 1                   | 1-2        | 2-3            |  |

| POS: 5 V on pin 1 and 12 V on pin 9 | 2-3        | 2-3            |  |

|                                     |            |                |  |

|                                     |            |                |  |

| COM2 RS-232 Mode                    | JV3        | JV4            |  |

| COM2 RS-232 Mode<br>Standard        | JV3<br>1-2 | <b>JV4</b> 1-2 |  |

|                                     |            |                |  |

| Standard                            | 1-2        | 1-2            |  |

| Standard<br>POS : 12 V on pin 9     | 1-2        | 1-2<br>1-2     |  |

### Flash Disk

Compact Flash Disk

#### Installation Instructions

- 1. Make sure the Single Board Computer is powered OFF.

- Plug the Compact Flash Typel/II device into its socket. Verify the direction is correct on Secondary IDE which is located in the back of SBC.

- 3. Powre up the system

For more information on Compact Flash disk, visit Pretech Web site at

http://www.pretech.com

where you can find the utilities manual, data sheets and application notes. In addition, you can find the latest Compact Flash disk utilities.

# **Ethernet Connectors**

## LAN Port Signals (LAN1, LAN2 & LAN3)

Connector: **LAN1, 2 & 3**Type: Onboard 10-pin header

| Pin | Description | Pin | Description |  |

|-----|-------------|-----|-------------|--|

| 1   | TX+         | 2   | TX-         |  |

| 3   | RX+         | 4   | N/C         |  |

| 5   | N/C         | 6   | RX-         |  |

| 7   | N/C         | 8   | N/C         |  |

| 9   | GND         | 10  | GND         |  |

### **LAN LED Connector (LANLED)**

Connector: LANLED

| Pin  | Description              |

|------|--------------------------|

| LAN1 |                          |

| 1-2  | Link (on) Activity flash |

| 3-4  | 100 (on) / 10 (off)      |

| LAN2 |                          |

| 5-6  | Link (on) Activity flash |

| 7-8  | 100 (on) / 10 (off)      |

# Power Connector

#### **ATX Feature Connector**

ATX Feature Connector:ATX1

Type: onboard 3-pin Wafer connector

| Pin | Description |

|-----|-------------|

| 1   | PS-ON       |

| 2   | GND         |

| 3   | 5VSB        |

ATX Power Connector (PWR1)

Connector : PWR1

Type: 4 pin

| Pin | Description |

|-----|-------------|

| 1   | +5V         |

| 2   | GND         |

| 3   | GND         |

| 4   | +12V        |

### **CPU Fan Connector**

Connector : CPUF1

Type: onboard 3-pin wafer connector

| Pin | Description |  |

|-----|-------------|--|

| 1   | FAN_CTL     |  |

| 2   | +5V         |  |

| 3   | GND         |  |

# Interface Connectors HDD, FDD

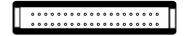

# Floppy Disk Drive Connector

2

Connector: FDD

Type: onboard 34-pin box header

| Pin | Description | Pin | Description            |

|-----|-------------|-----|------------------------|

| 1   | GND         | 2   | DRIVE DENSITY SELECT 0 |

| 3   | GND         | 4   | NC                     |

| 5   | GND         | 6   | DRIVE DENSITY SELECT 1 |

| 7   | GND         | 8   | #INDEX                 |

| 9   | GND         | 10  | #MOTOR ENABLE A        |

| 11  | GND         | 12  | #DRIVER SELECT B       |

| 13  | GND         | 14  | #DRIVER SELECT A       |

| 15  | GND         | 16  | #MOTOR ENABLE B        |

| 17  | GND         | 18  | #DIRECTION             |

| 19  | GND         | 20  | #STEP                  |

| 21  | GND         | 22  | #WRITE DATA            |

| 23  | GND         | 24  | #WRITE GATE            |

| 25  | GND         | 26  | #TRACK 0               |

| 27  | GND         | 28  | #WRITE PROTECT         |

| 29  | GND         | 30  | #READ DATA             |

| 31  | GND         | 32  | #HEAD SELECT           |

| 33  | GND         | 34  | #DISK CHANGE           |

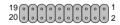

# **Enhanced IDE Connector**

Connector: IDE1

Type: One onboard 44-pin box headers, primary IDE

| Pin | Description | Pin | Description      |

|-----|-------------|-----|------------------|

| 1   | #RESET      | 2   | GND              |

| 3   | D7          | 4   | D8               |

| 5   | D6          | 6   | D9               |

| 7   | D5          | 8   | D10              |

| 9   | D4          | 10  | D11              |

| 11  | D3          | 12  | D12              |

| 13  | D2          | 14  | D13              |

| 15  | D1          | 16  | D14              |

| 17  | D0          | 18  | D15              |

| 19  | GND         | 20  | NC               |

| 21  | REQ         | 22  | GND              |

| 23  | #IOW        | 24  | GND              |

| 25  | #IOR        | 26  | GND              |

| 27  | #IORDY      | 28  | IDESEL           |

| 29  | #DACK       | 30  | GND              |

| 31  | IRQ         | 32  | NC               |

| 33  | ADDR1       | 34  | CBLID            |

| 35  | ADDR0       | 36  | ADDR2            |

| 37  | #CS0        | 38  | #CS1(#HD SELET1) |

| 39  | #ACT        | 40  | GND              |

| 41  | Vcc         | 42  | Vcc              |

| 43  | GND         | 4 4 | GND              |

|     |             |     |                  |

# **Flat Panel Connector**

# LCD Interface Connector

LCD1 connector is defined for TTL panel supporting 24-bit only. LCD2 connector is defined for LVDS panel for one channel and TTL panel up to 36bit (More than 24bit of TTL panel 24bit needs to use both connector LCD1 & LCD2).

Connector: LCD1

Type: Onboard DF13-40DS connector

LCD1 pin Assignment

| Pin    | Description | Pin | Description |

|--------|-------------|-----|-------------|

| 1      | LCD Power   | 2   | Ground      |

| <br>3  | LCD Power   | 4   | Ground      |

| 5      | Ground      | 6   | FPD0        |

| 7      | FPD1        | 8   | FPD2        |

| <br>9  | FPD3        | 10  | FPD4        |

| 11     | FPD5        | 12  | FPD6        |

| <br>13 | FPD7        | 14  | Ground      |

| 15     | Ground      | 16  | FPD8        |

| 17     | FPD9        | 18  | FPD10       |

| <br>19 | FPD11       | 20  | FPD12       |

| 21     | FPD13       | 22  | FPD14       |

| <br>23 | FPD15       | 24  | Ground      |

| 25     | Ground      | 26  | FPD16       |

| 27     | FPD17       | 28  | FPD18       |

| <br>29 | FPD19       | 30  | FPD20       |

| 31     | FPD21       | 32  | FPD22       |

| <br>33 | FPD23       | 34  | Ground      |

| 35     | Ground      | 36  | FP_DE       |

| 37     | FP_VS       | 38  | FP_CLK      |

| <br>39 | FP_HS       | 40  | Ground      |

|        |             |     |             |

Connector : LCD2

Type: Onboard DF13-30DS connectors

### LCD2 pin Assignment

| 1      | LCD Power | 2  | Ground |

|--------|-----------|----|--------|

| 3      | LCD Power | 4  | YOM    |

| 5      | Ground    | 6  | YOP    |

| 7      | FPD24     | 8  | Ground |

| 9      | FPD25     | 10 | Y1M    |

| 11     | FPD26     | 12 | Y1P    |

| 13     | FPD27     | 14 | Ground |

| 15     | FPD28     | 16 | Y2M    |

| 17     | FPD29     | 18 | Y2P    |

| <br>19 | FPD30     | 20 | Ground |

| 21     | FPD31     | 22 | YCM    |

| 23     | FPD32     | 24 | YCP    |

| 25     | FPD33     | 26 | Ground |

| 27     | FPD34     | 28 | NC     |

| 29     | FPD35     | 30 | NC     |

|        |           |    |        |

#### LCD Inventor Connector: INV

#### INV pin Assignment

| Pin | Description |

|-----|-------------|

| 1   | +12V        |

| 2   | Ground      |

| 3   | FP_ON       |

| 4   | VEEP (5V)   |

| 5   | Ground      |

# **Peripheral Port**

#### **Parallel Port**

Connector: LPT1

Type: onboard 26-pin box header

| 26 000000000000 14 |

|--------------------|

|--------------------|

LPT1

| Pin | Description  | Pin | Description   |

|-----|--------------|-----|---------------|

| 1   | #STROBE      | 14  | #AUTO FEED    |

| 2   | DATA0        | 15  | #ERROR        |

| 3   | DATA1        | 16  | #INITIALIZE   |

| 4   | DATA2        | 17  | #SELECT INPUT |

| 5   | DATA3        | 18  | GND           |

| 6   | DATA4        | 19  | GND           |

| 7   | DATA5        | 20  | GND           |

| 8   | DATA6        | 21  | GND           |

| 9   | DATA7        | 22  | GND           |

| 10  | #ACKNOWLEDGE | 23  | GND           |

| 11  | BUSY         | 24  | GND           |

| 12  | PAPER EMPTY  | 25  | GND           |

| 13  | SELECT       | 26  | GND           |

#### **USB Ports**

Connector: USB1, USB2

Type:onboard Two 10-pin box headers for four USB ports

USB

| Pin | Description | Pin | Description |

|-----|-------------|-----|-------------|

| 1   | VCC         | 2   | VCC         |

| 3   | DATA-       | 4   | DATA-       |

| 5   | DATA+       | 6   | DATA+       |

| 7   | GND         | 8   | GND         |

| 9   | GND         | 10  | GND         |

#### SIR

Connector: SIR

Type: onboard 5-pin header

|      | <b>→</b> (•) |

|------|--------------|

|      | ∾ 🕝          |

| 0.10 | ω 💿          |

| SIR  | Q 4          |

|      | m (a)        |

| Pin | Description | Pin | Description |

|-----|-------------|-----|-------------|

| 1   | Vcc         | 2   | NC          |

| 3   | IRRX        | 4   | GND         |

| 5   | IRTX        |     |             |

### **CRT SVGA**

Connector: VGA

Type: internal 16-pin header connector on bracket

| P | in | Description | Pin | Description | Pin | Description |

|---|----|-------------|-----|-------------|-----|-------------|

| 1 |    | RED         | 6   | GND         | 11  | NC          |

| 2 |    | GREEN       | 7   | GND         | 12  | VDDAT       |

| 3 |    | BLUE        | 8   | GND         | 13  | HSYNC       |

| 4 |    | NC          | 9   | Vcc         | 14  | VSYNC       |

| 5 |    | GND         | 10  | GND         | 15  | VDCLK       |

| 1 | 6  | NC          |     |             |     |             |

# PS/2 Keyboard & Mouse

KBM O

Connector: KBM

Type: external 6-pin Mini DIN connector on bracket

| Pin | Description | Pin | Description |

|-----|-------------|-----|-------------|

| 1   | KB-DATA     | 2   | MS-DATA     |

|     |             |     |             |

| 5   | GND         | 6   | GND         |

| 7   | Vcc         | 8   | Vcc         |

| 9   | KB-CLK      | 10  | MS-CLK      |

#### COM1 Port with RS-232C Mode

Connector: COM1

Type: onboard 10-pin box header

| Pin | Description | Pin | Description |  |

|-----|-------------|-----|-------------|--|

| 1   | DCD         | 2   | RXD         |  |

| 3   | TXD         | 4   | DTR         |  |

| 5   | GND         | 6   | DSR         |  |

| 7   | RTS         | 8   | CTS         |  |

| 9   | RI          | 10  | NC          |  |

#### COM2 Port with RS-232C Mode

Connector: COM2

Type: onboard 10-pin box header

| Pin | Description | Pin | Description |  |

|-----|-------------|-----|-------------|--|

| 1   | DCD         | 2   | RXD         |  |

| 3   | TXD         | 4   | DTR         |  |

| 5   | GND         | 6   | DSR         |  |

| 7   | RTS         | 8   | CTS         |  |

| 9   | RI          | 10  | NC          |  |

#### COM2 Port with RS-422/485 Mode

Connector: COM2

Type: onboard 10-pin box header

#### RS-422 Mode

| Pin | Description | Pin | Description |  |

|-----|-------------|-----|-------------|--|

| 1   | TX+         | 2   | TX-         |  |

| 3   | NC          | 4   | NC          |  |

| 5   | NC          | 6   | NC          |  |

| 7   | NC          | 8   | RX+         |  |

| 9   | RX-         | 10  | NC          |  |

#### RS-485 Mode

Data+ of RS-485 is connected by pin-1

Data- of RS-485 is connected by pin-2

## **Audio Interface Port (AUDIO)**

Connector: AUDIO

Type: onboard 10-pin header

| Pin | Description | Pin | Description |

|-----|-------------|-----|-------------|

| 1   | LINEL       | 2   | LINER       |

| 3   | GND         | 4   | GND         |

| 5   | MIC         | 6   | NC          |

| 7   | GND         | 8   | GND         |

| 9   | LOOT-L      | 10  | LOOT-R      |

#### **CDROM audio interface (CDIN)**

Connector: CDIN

Type: onboard 4-pin boxheader

| Pin | Description | Pin | Description |

|-----|-------------|-----|-------------|

| 1   | CD Left     | 2   | GND         |

| 3   | GND         | 4   | CD Right    |

# 16-bit General Purpose I/O (DIO)

Connector: DIO

Type: Onboard 20-pin header

| Pin    | Description | Pin | Description |

|--------|-------------|-----|-------------|

| 1      | D00         | 2   | D01         |

| 3      | D02         | 4   | D03         |

| 5      | DO4         | 6   | D05         |

| 7      | D06         | 8   | D07         |

| <br>9  | GND         | 10  | GND         |

| 11     | DIO         | 12  | DI1         |

| 13     | DI2         | 14  | DI3         |

| 15     | DI4         | 16  | DI5         |

| 17     | DI6         | 18  | DI7         |

| <br>19 | +5V         | 20  | +12V        |

Output Port I/O Based Address: 208hex~20Fh; Pin1~Pin8 Input Port I/O Based Address: 200hex~207h; Pin11~Pin18

# **Switches and Indicators**

Connector: FRT

Type: onboard 20-pin header

| Pin         | Jumper | Description           |

|-------------|--------|-----------------------|

| 1-2         | PSON   | ATX soft power switch |

| 3-4         | RES    | reset function        |

| 5-6         | ESMI   | external SMI          |

| 7-8         | HLED   | Hard Disk LED         |

| 13,15,17,19 | Speak  | exteranal speaker     |

| 16,18,20    | PWRLED | power LED             |

Connector: SPEAK

| Pin | Description |

|-----|-------------|

| 13  | Speak +     |

| 15  | NC          |

| 17  | NC          |

| 19  | Speak -     |

Connector: PWRLED

| Pin | Description |

|-----|-------------|

| 16  | LED -       |

| 18  | NC          |

| 20  | LED +       |

# System Resources

### **Interrupt Assignment**

| IRQ Address | Description                       |

|-------------|-----------------------------------|

| 0           | System Timer                      |

| 1           | Keyboard (KB output buffer full)  |

| 2           | Programmable Interrupt Controller |

| 3           | Serial Port 2 (COM2)              |

| 4           | Serial Port 1 (COM1)              |

| 5           | Resvered                          |

| 6           | Floppy controller                 |

| 7           | Parallel Port 1                   |

| 8           | Real-Time Clock                   |

| 9           | USB                               |

| 10          | Ethernet 1                        |

| 11          | Ethernet 2                        |

| 12          | PS/2 Mouse                        |

| 13          | Numeric data processor            |

| 14          | Primary IDE Controller            |

| 15          | Secondary IDE Controller          |

### I/O Address Space

| Adress      | Description                   |

|-------------|-------------------------------|

| 0000 - 000F | DMA Controller                |

| 0010 - 001F | Motherboard Resources         |

| 0020 - 0021 | PIC                           |

| 0022 - 003F | Motherboard Resources         |

| 0040 - 0043 | System Timer                  |

| 0044 - 005F | Motherboard Resources         |

| 0060 - 0060 | Keyboard                      |

| 0061 - 0061 | Systems Speaker               |

| 0062 - 0063 | Motherboard Resources         |

| 0064 - 0064 | Keyboard                      |

| 0065 - 006F | Motherboard Resources         |

| 0070 - 0071 | System CMOS / Real time clock |

| 0072 - 0080 | Motherboard Resources         |

| 0081 - 0083 | DMA Controller                    |  |  |

|-------------|-----------------------------------|--|--|

| 008F - 0091 | DMA Controller                    |  |  |

| 00A0 - 00A1 | PIC                               |  |  |

| 00A2 - 00BF | Motherboard Resources             |  |  |

| 00E0 - 00EF | Motherboard Resources             |  |  |

| 00C0 - 00DF | DMA Controller                    |  |  |

| 00F0 - 00FF | Numeric Data Processor            |  |  |

| 0170 - 0177 | VIA Bus Master PCI IDE Controller |  |  |

| 01F0 - 01F7 | VIA Bus Master PCI IDE Controller |  |  |

| 02F8 - 02FF | Communications Port B             |  |  |

| 0376 - 0376 | VIA Bus Master PCI IDE Controller |  |  |

| 0378 - 037F | Printer Port                      |  |  |

| 03F0 - 03F5 | Floppy Disk Controller            |  |  |

| 03F6 - 03F6 | Intel Ultra ATA Controller        |  |  |

| 03F7 - 03F7 | Floppy Disk Controller            |  |  |

| 03F8 - 03FF | C0M1                              |  |  |

| 0400 - 048F | Motherboard Resources             |  |  |

| 0480 - 048F | Motherboard Resources             |  |  |

| 04D0 - 04D1 | PCI bus                           |  |  |

# PCI Bus Map

| Functino | Device ID | INT# | GNT# |  |

|----------|-----------|------|------|--|

| LAN1     | AD19      | INTB | GNT0 |  |

| LAN2     | AD20      | INTC | GNT1 |  |

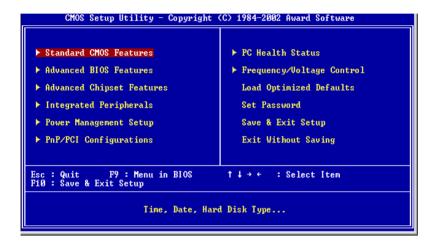

# **AWARD BIOS Setup**

The SBC uses the Award PCI/ISA BIOS ver 6.0 for the system configuration. The Award BIOS setup program is designed to provide the maximum flexibility in configuring the system by offering various options which could be selected for end-user requirements. This chapter is written to assist you in the proper usage of these features.

To access AWARD PCI/ISA BIOS Setup program, press <Del> key. The Main Menu will be displayed at this time.

Once you enter the AwardBIOS<sup>TM</sup> CMOS Setup Utility, the Main Menu will appear on the screen. The Main Menu allows you to select from several setup functions and two exit choices. Use the arrow keys to select among the items and press <Enter> to accept and enter the sub-menu.

#### **Setup Items**

The main menu includes the following main setup categories. Recall that some systems may not include all entries.

#### Standard CMOS Features

Use this menu for basic system configuration.

#### Advanced BIOS Features

Use this menu to set the Advanced Features available on your system.

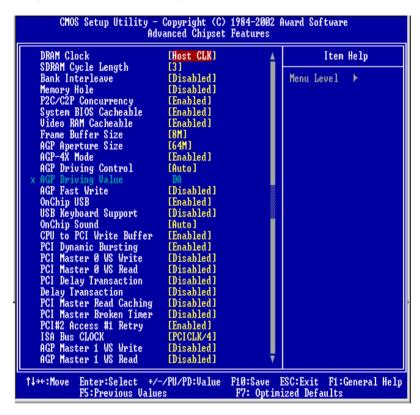

#### **Advanced Chipset Features**

Use this menu to change the values in the chipset registers and optimize your system's performance.

#### Integrated Peripherals

Use this menu to specify your settings for integrated peripherals.

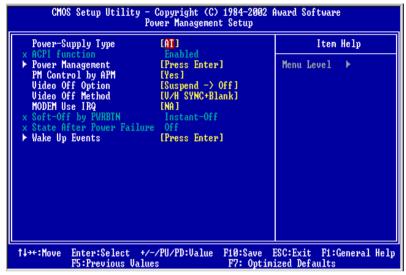

#### **Power Management Setup**

Use this menu to specify your settings for power management.

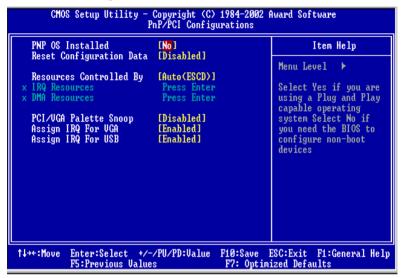

#### PnP / PCI Configuration

This entry appears if your system supports PnP / PCI.

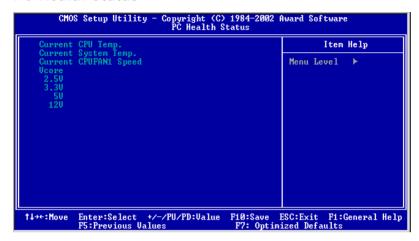

#### PC Health Status

This entry appears CPU temperature for the systeml.

#### Frequency/Voltage Control

Use this menu to specify your settings for frequency/voltage control.

#### Load Optimized Defaults

Use this menu to load the BIOS default values that are factory settings for optimal performance system operations. While Award has designed the custom BIOS to maximize performance, the factory has the right to change these defaults to meet their needs.

#### Set Password

Use this menu to set User and Supervisor Passwords.

#### Save & Exit Setup

Save CMOS value changes to CMOS and exit setup.

#### **Exit Without Save**

Abandon all CMOS value changes and exit setup.

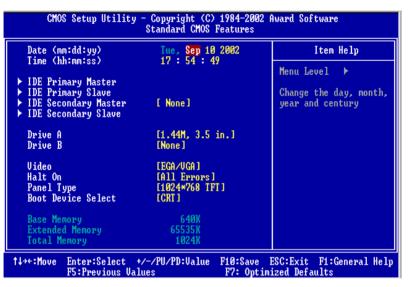

#### Standard CMOS Setup

$\uparrow \downarrow \rightarrow \leftarrow : \texttt{Move Enter} : \texttt{Select +/-/PU/PD} : \texttt{Value F10} : \texttt{Save ESC} : \texttt{Exit F1} : \texttt{General Help F5} : \texttt{Previous Values F6} : \texttt{Fail-SAfe Defaults F7} : \texttt{Optimized Defaults}$

#### Date

The BIOS determines the day of the week from the other date information; this field is for information only.

#### Time

The time format is based on the 24-hour military-time clock. For example, 1 p.m. is 13:00:00. Press the « or ( key to move to the desired field . Press the PgUp or PgDn key to increment the setting, or type the desired value into the field.

# IDE Primary Master/Slave IDE Secondary Master/Slave

Options are in sub menu (see page 30)

#### Drive A, B

Select the correct specifications for the diskette drive(s) installed in the computer.

None: No diskette drive installed

**360K**; 5.25 in 5-1/4 inch PC-type standard drive **1.2M**; 5.25 in 5-1/4 inch AT-type high-density drive

**720K**; 3.5 in 3-1/2 inch double-sided drive **1.44M**; 3.5 in 3-1/2 inch double-sided drive **2.88M**: 3.5 in 3-1/2 inch double-sided drive **Video** Select the type of primary video subsystem in your computer. The BIOS usually detects the correct video type automatically. The BIOS supports a secondary video subsystem, but you do not select it in Setup.

**Halt On** During the power-on self-test (POST), the computer stops if the BIOS detects a hardware error. You can tell the BIOS to ignore certain errors during POST and continue the boot-up process. These are the selections:

No errors POST does not stop for any errors.

All errors If the BIOS detects any non-fatal error, POST stops and

prompts you to take corrective action.

All, But Keyboard POST does not stop for a keyboard error, but stops for

all other errors.

All, But Diskette POST does not stop for diskette drive errors, but stops

for all other errors.

All, But Disk/Key POST does not stop for a keyboard or disk error, but

stops for all other errors.

Panel Type Select the different panel type to run the system. Four various

resolutions for TFT type and two for DSTN.

**Boot Device** This item allows you to select the different devices for boot up function

# IDE Harddisk Setup (submenu)

| IDE HDD Auto-Detection            | Press Enter | Item Help     |

|-----------------------------------|-------------|---------------|

| IDE Primary Master<br>Access Mode | [Auto]      | Menu Level ▶▶ |

| Capacity                          | 0 MB        |               |

| Cylinder                          | 0           |               |

| Head                              | 0           |               |

| Precomp                           | 0           |               |

| Landing Zone                      | 0           |               |

| Sector                            | 0           |               |

|                                   |             |               |

$<sup>\</sup>uparrow\downarrow\rightarrow\leftarrow$ : Move Enter: Select +/-/PU/PD: Value F10: Save ESC: Exit F1: General Help F5: Previous Values F6: Fail-SAfe Defaults F7: Optimized Defaults

# **IDE HDD Auto-detection**

Press Enter to auto-detect the HDD on this channel. If detection is successful, it fills the remaining fields on this menu.

# **IDE Primary Master**

Selecting 'manual' lets you set the remaining fields on this screen. Selects the type of fixed disk. "User Type" will let you select the number of cylinders, heads, etc. Note: PRECOMP=65535 means NONE!

# Capacity

Disk drive capacity (Approximated). Note that this size is usually slightly greater than the size of a formatted disk given by a disk checking program.

# Access Mode

Normal, LBA, Large or Auto Choose the access mode for this hard disk

The following options are selectable only if the 'IDE Primary Master' item is set to 'Manual'

**Cylinder** Min = 0 Max = 65535 Set the number of cylinders for this hard disk.

**Head** Min = 0 Max = 255 Set the number of read/write heads

**Precomp** Min = 0 Max = 65535

\*\*\*\* Warning: Setting a value of 65535 means no hard disk

Landing zone Min = 0 Max = 65535

\*\*\*\* Warning: Setting a value of 65535 means no hard disk

Sector Min = 0 Max = 255

Number of sectors per track

We recommend that you select Type "AUTO" for all drives. The BIOS will auto-detect the hard disk drive and CD-ROM drive at the POST stage.

If your hard disk drive is a SCSI device, please select "None" for your hard drive setting.

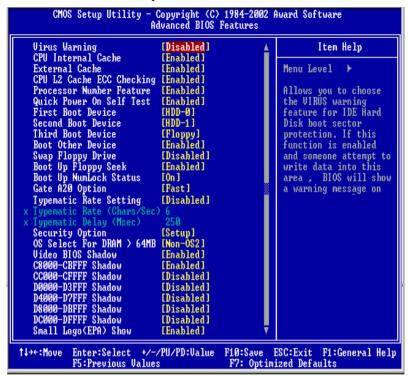

# **BIOS Features Setup**

$\uparrow \downarrow \rightarrow \leftarrow : Move \ \, Enter: Select \, +/-/PU/PD: Value \ \, F10: Save \ \, ESC: Exit \ \, F1: General \ \, Help \\ F5: Previous Values \ \, F6: Fail-SAfe Defaults \ \, F7: Optimized Defaults$

# Virus Warning

Allows you to choose the VIRUS Warning feature for IDE Hard Disk boot sector protection. If this function is enabled and someone attempt to write data into this area, BIOS will show a warning message on screen and beep.

Enabled Activates automatically when the system boots up causing a warning message to appear when anything attempts to access the boot sector or hard disk partition table.

Disabled No warning message will appear when anything attempts to access the boot sector or hard disk partition table.

#### CPU Internal Cache/External Cache

These two categories speed up memory access. However, it depends on CPU/chipset design. Enabled: Enable cache, Disabled: Disable cache

### CPU L2 Cache ECC Checking

This item allows you to enable/disable CPU L2 Cache ECC checking. The choice: Enabled. Disabled.

#### **Processor Number Feature**

This feature appears when a a Pentium III processor is installed. It enables you enables you to control whether the Pentium III's serial number can be read by external programs. The choice: Enabled. Disabled

### Quick Power On Self Test

This category speeds up Power On Self Test (POST) after you power up the computer. If it is set to Enable, BIOS will shorten or skip some check items during POST. Enabled: Enable quick POST. Disabled: Normal POST

#### First/Second/Third/Other Boot Device

The BIOS attempts to load the operating system from the devices in the sequence selected in these items. The choices are: Floppy, LS/ZIP, HDD, SCSI, CDROM, Disabled.

### Swap Floppy Drive

If the system has two floppy drives, you can swap the logical drive name assignments. The choice: Enabled/Disabled.

# **Boot Up Floppy Seek**

Seeks disk drives during boot up. Disabling speeds boot up. The choice: Enabled/Disabled

# Boot Up NumLock Status

Select power on state for NumLock. The choice: Enabled/Disabled.

#### Gate A20 Option

Select if chipset or keyboard controller should control GateA20.

Normal A pin in the keyboard controller controls GateA20

Fast Lets chipset control GateA20

## Typematic Rate Setting

Key strokes repeat at a rate determined by the keyboard controller. When enabled, the typematic rate and typematic delay can be selected.

The choice: Enabled/Disabled.

## Typematic Rate (Chars/Sec)

Sets the number of times a second to repeat a key stroke when you hold the key down. The choice: 6, 8, 10, 12, 15, 20, 24, 30.

# Typematic Delay (Msec)

Sets the delay time after the key is held down before it begins to repeat the keystroke. The choice: 250, 500, 750, 1000.

### Security Option

Select whether the password is required every time the system boots or only when you enter setup.

System The system will not boot and access to Setup will be denied if the correct password is not entered at the prompt.

Setup The system will boot, but access to Setup will be denied if the correct password is not entered at the prompt.

Note To disable security, select PASSWORD SETTING at Main Menu and then you will be asked to enter password. Do not type anything and just press <Enter>, it will disable security. Once the security is disabled, the system will boot and you can enter Setup freely.

#### OS Select For DRAM > 64MB

Select the operating system that is running with greater than 64MB of RAM on the system.The choice: Non-OS2, OS2.

#### Video BIOS Shadow

Enabled this copies the video BIOS from ROM to RAM. effectively enhancing performance, and reducing the amount of upper memory available by 32KB (the C0000~C7FFF area of memory between 640 KB and 1 MB is used).

#### C8000-CBFFF Shadow

Enabling any of the C8000~CBFFF segments allows components to move their firmware into these upper memory segments. However your computer can lock-up doing so, because some devices don't like being shadowed at those particular 16 KB segments of upper memory.

Note - In Windows 95, double click 'Computer' within Device Manager and select 'Memory'. This will tell you what segments (if any) are being shadowed For DOS you can use MSD.EXE to see what segments are claimed. CC000-CFFFF - D0000-D3FFF - D4000-D7FFF - D8000-DBFFF and DC000-DFFFF - Same as above.

# **Chipset Features Setup**

#### DRAM Clock

This item allows you to set the DRAM Clock. Options are Host CLK, HCLK+33M or HCLK-33M. Please set the item according to the Host (CPU) Clock and DRAM Clock

# SDRAM Cycle Length

This feature is similar to SDRAM CAS Latency Time. It controls the time delay (in clock cycles - CLKs) that passes before the SDRAM starts to carry out a read command after receiving it. This also determines the number of CLKs for the completion of the first part of a burst transfer. Thus, the lower the cycle length, the faster the transaction. However, some SDRAM cannot handle the lower cycle length and may become unstable. So, set the SDRAM Cycle Length to 2 for optimal performance if possible but increase it to 3 if your system becomes unstable.

#### Bank Interleave

This feature enables you to set the interleave mode of the SDRAM interface. Interleaving allows banks of SDRAM to alternate their refresh and access cycles. One bank will undergo its refresh cycle while another is being accessed. This improves performance of the SDRAM by masking the refresh time of each bank. A closer examination of interleaving will reveal that since the refresh cycles of all the SDRAM banks are staggered, this produces a kind of pipelining effect. If there are 4 banks in the system, the CPU can ideally send one data request to each of the SDRAM banks in consecutive clock cycles. This means in the first clock cycle, the CPU will send an address to Bank 0 and then send the next address to Bank 1 in the second clock cycle before sending the third and fourth addresses to Banks 2 and 3 in the third and fourth clock cycles respectively. Each SDRAM DIMM consists of either 2 banks or 4 banks. 2-bank SDRAM DIMMs use 16Mbit SDRAM chips and are usually 32MB or less in size. 4-bank SDRAM DIMMs, on the other hand, usually use 64Mbit SDRAM chips though the SDRAM density may be up to 256Mbit per chip. All SDRAM DIMMs of at least 64MB in size or greater are 4-hanked in nature

If you are using a single 2-bank SDRAM DIMM, set this feature to 2-Bank. But if you are using two 2-bank SDRAM DIMMs, you can use the 4-Bank option as well. With 4-bank SDRAM DIMMs, you can use either interleave options. Naturally, 4-bank interleave is better than 2-bank interleave so if possible, set it to 4-Bank. Use 2-Bank only if you are using a single 2-bank SDRAM DIMM. Notethat it is recommends that SDRAM bank interleaving be disabled if 16Mbit SDRAM DIMMs are used.

#### Memory Hole

Enabling this feature reserves 15MB to 16MB memory address space to ISA expansion cards that specifically require this setting. This makes the memory from 15MB and up unavailable to the system. Expansion cards can only access memory up to 16MB.

### P2C/C2P Concurrency

When Disabled, CPU bus will be occupied during the entire PCI operation period.

### System BIOS Cacheable

Allows the system BIOS to be cached for faster system performance.

#### Video RAM Cacheable

This item allows you to "Enabled" or "Disabled" on Video RAM Cacheable.

#### Frame Buffer Size

This item defines the amount of system memory that will be shared and uses as video memory.

# AGP Aperture Size

Options: 4, 8, 16, 32, 64, 128, 256

This option selects the size of the AGP aperture. The aperture is a portion of the PCI memory address range dedicated as graphics memory address space. Host cycles that hit the aperture range are forwarded to the AGP without need for translation. This size also determines the maximum amount of system RAM that can be allocated to the graphics card for texture storage.

AGP Aperture size is set by the formula: maximum usable AGP memory size x 2 plus 12MB. That means that usable AGP memory size is less than half of the AGP aperture size. That's because the system needs AGP memory (uncached) plus an equal amount of write combined memory area and an additional 12MB for virtual addressing. This is address space, not physical memory used. The physical memory is allocated and released as needed only when Direct3D makes a "create non-local surface" call.

#### AGP-4X Mode

Set to Enabled if your AGP card supports the 4X mode, which transfers video data at 1066MB/s.

# **AGP Driving Control**

This item is use for control AGP drive strength. Auto: Setup AGP drive strength by default setting. Manual: Setup AGP drive strength by manual setting.

# **AGP Driving Value**

Key in a HEX number to control AGP output buffer drive strength. Min = 00, Max = FF.

### **AGP Fast Write**

To enable this function can increase VGA performance on graphic designed.

# Panel Type

This item allows you to select different of Panel type.

#### **Boot Device Select**

This item allows you to select different type of devices for boot up.

## OnChip USB

If your system contains a Universal Serial Bus controller and you have a USB peripheral, select Enabled. The next option will become available.

### **USB Keyboard Support**

This item lets you enable or disable the USB keyboard driver within the onboard BIOS.

#### OnChip Sound

This menu can access the sound controller automaticlly

#### CPU to PCI Write Buffer

This controls the CPU write buffer to the PCI bus. If this buffer is disabled, the CPU writes directly to the PCI bus. Although this may seem like the faster and thus, the better method, this isn't true. Because the CPU bus is faster than the PCI bus, any CPU writes to the PCI bus has to wait until the PCI bus is ready to receive data. This prevents the CPU from doing anything else until it has completed sending the data to the PCI bus. Enabling the buffer enables the CPU to immediately write up to 4 words of data to the buffer so that it can continue on another task without waiting for those 4 words of data to reach the PCI bus. The data in the write buffer will be written to the PCI bus when the next PCI bus read cycle starts. The difference here is that it does so without stalling the CPU for the entire CPU to PCI transaction. Therefore, it's recommended that you enable the CPU to PCI write buffer.

# **PCI Dynamic Bursting**

When enabled, data transfer on the PCI bus, where possible, make use of the high-performance PCI bust protocol, in which greater amounts of data are transferred at a single command.

#### PCI Master 0 WS Write

This function determines whether there's a delay before any writes to the PCI bus. If this is enabled, then writes to the PCI bus are executed immediately (with zero wait states), as soon as the PCI bus is ready to receive data. But if it is disabled, then every write transaction to the PCI bus is delayed by one wait state. Normally, it's recommended that you enable this for faster PCI performance. However, disabling it may be useful when overclocking the PCI bus results in instability. The delay will generally improve the overclockability of the PCI bus.

# PCI Master 0 WS Read

This function determines whether there's a delay before any writes to the PCI bus. If this is enabled, then read to the PCI bus are executed immediately (with zero wait states), as soon as the PCI bus is ready to receive data. But if it is disabled, then every read transaction to the PCI bus is delayed by one wait state. Normally, it's recommended that you enable this for faster PCI performance. However, disabling it may be useful when overclocking the PCI bus results in instability. The delay will generally improve the overclockability of the PCI bus.

# **PCI Delay Transaction**

The chipset has an embedded 32-bit posted write buffer to support delay transactions cycles. Select Enabled to support compliance with PCI specification version 2.1.

### **Delay Transaction**

The chipset has an embedded 32-bit posted write buffer to support delay transactions cycles. Select Enabled to support compliance with PCI specification version 2.1.

# **PCI Master Read Caching**

To enable this function, the CPU L2 cache will be used to cache PCI master reads. This boosts the performance of PCI master. It's recommend to disable this feature

#### PCI Master Broken Timer

To enable this feature allows for slower PCI bus mastering expansion cards.

### PCI # 2 Access # 1 Retry

This BIOS feature is linked to the CPU to PCI Write Buffer. Normally, the CPU to PCI Write Buffer is enabled. All writes to the PCI bus are, as such, immediately written into the buffer, instead of the PCI bus. This frees up the CPU from waiting till the PCI bus is free. The data are then written to the PCI bus when the next PCI bus cycle starts.

There's a possibility that the buffer write to the PCI bus may fail. When that happens, this BIOS option determines if the buffer write should be reattempted or sent back for arbitration. If this BIOS option is enabled, then the buffer will attempt to write to the PCI bus until successful. If disabled, the buffer will flush its contents and register the transaction as failed. The CPU will have to write again to the write buffer. It is recommended that you enable this feature unless you have many slow PCI devices in your system. In that case, disabling this feature will prevent the generation of too many retries which may severely tax the PCI bus.

### ISA Bus Clock

Allows you to set the speed of the ISA bus in fractions fo the PCI bus speed, so if the PCI bus is operating at its theoretical maximum, 33Mhz, PCICLK/3 would yield an ISA speed of 11Mhz. The choices: 7.159Mhz, PCICLK/4 and PCICLK/3.

#### AGP Master 1 WS Write

By default, the AGP busmastering device waits for at least 2 wait states or AGP clock cycles before it starts a write transaction. This BIOS option allows you to reduce the delay to only 1 wait state or clock cycle. For better AGP write performance, enable this option but disable it if you experience weird graphical anomalies like wireframe effects and pixel artifacts after enabling this option.

# AGP Master 1 WS Read

By default, the AGP busmastering device waits for at least 2 wait states or AGP clock cycles before it starts a read transaction. This BIOS option allows you to reduce the delay to only 1 wait state or clock cycle. For better AGP read performance, enable this option but disable it if you experience weird graphical anomalies like wireframe effects and pixel artifacts after enabling this option.

# **Integrated Peripherals**

$\uparrow \downarrow \rightarrow \leftarrow : \texttt{Move Enter} : \texttt{Select +/-/PU/PD} : \texttt{Value F10} : \texttt{Save ESC} : \texttt{Exit F1} : \texttt{General Help F5} : \texttt{Previous Values F6} : \texttt{Fail-SAfe Defaults F7} : \texttt{Optimized Defaults}$

#### OnChip IDE Channel 0/1

Select "Enabled" to activate each on-board IDE channel separately, Select "Disabled", if you install an add-on IDE Control card

#### **IDE Prefetch Mode**

Enable prefetching for IDE drive interfaces that support its faster drive accesses. If you are getting disk drive errors, change the setting to omit the drive interface where the errors occur. Depending on the configuration of your IDE subsystem, this field may not appear, and it does appear when the Internal PCI/IDE filed, above, is Disabled.

# Primary & Secondary Master/Slave PIO

These four PIO fields let you set a PIO mode (0-4) for each of four IDE devices. When under "Auto" mode, the system automatically set the best mode for each device

# Primary & Secondary Master/Slave UDMA

When set to "Auto" mode, the system will detect if the hard drive supports Ultra DMA mode.

### Init Display First

Select "AGP" or "PCI Slot" for system to detect first when boot-up.

#### **IDE HDD Block Mode**

This feature enhances disk performance by allowing multi-sector data transfers and eliminates the interrupt handling time for each sector.

#### Onboard LAN Boot ROM

This feature allows you to run LAN Boot function. Select "Disnabled" not to access this function

#### Onboard LAN1

Select "Enabled" if your system contains a LAN1 port.

#### Onboard LAN2

Select "Enabled" if your system contains a LAN1 port.

### **Onboard FDD Controller**

Select "Enabled" to activate the on-board FDD Select "Disabled" to activate an add-on FDD

# Onboard Serial Port 1 & 2

Select an address and corresponding interrupt for the first/second serial port. The default value for the first serial port is "3F8/IRQ4" and the second serial port is "2F8/IRQ3".

### **Onboard Parallel Port**

Select address and interrupt for the Parallel port.

### **Onboard Parallel Mode**

Select an operating mode for the parallel port. Mode options are Normal, EPP, ECP ECP/EPP.

# ECP Mode Use DMA

Select a DMA channel if parallel Mode is set as ECP, ECP/EPP.

### Parallel Port EPP Type

Select a EPP Type if parallel Port is set as EPP, ECP/EPP.

# Onboard Legacy Audio

Configuration options: Enabled and Disabled. When Enabled, select additional settings for SoundBlaster Compatibillity and MPU-401 functionallity

# **Power Management Setup**

$\uparrow \downarrow \rightarrow \leftarrow : \texttt{Move Enter} : \texttt{Select +/-/PU/PD} : \texttt{Value F10} : \texttt{Save ESC} : \texttt{Exit F1} : \texttt{General Help F5} : \texttt{Previous Values F6} : \texttt{Fail-SAfe Defaults F7} : \texttt{Optimized Defaults}$

# **ACPI Function**

Select Enabled only if your computer's operating system supports ACPI (the Advanced Configuration and Power Interface) specification. Currently, Windows 98 and Windows2000 support ACPI.

# **Power Management**

There are 4 selections for Power Management, 3 of which have fixed mode :

| Disabled (default) | No power management. Disables all four modes.                                                                         |

|--------------------|-----------------------------------------------------------------------------------------------------------------------|

| Min. Power Saving  | Minimum power management. Doze Mode = 1 hr.,<br>Standby Mode = 1 hr., Suspend Mode = 1 hr.,                           |

| Max. Power Saving  | Maximum power management ONLY AVAILABLE FOR SL CPU's Doze Mode = 1 min., Standby Mode = 1 min., Suspend Mode = 1 min. |

| User Defined       | Allows you to set each mode individually. When not disabled, each of the ranges are from 1 min. to 1 hr.              |

HDD Power Down is always set independently

# PM Control By APM

When enabled, an Advanced power Management device will be activated to enhance the Max. Power Saving mode and stop the CPU internal clock. If the Max. Power Saving is not enabled, this will be preset to No.

## Video Off Option

Controls what causes the display to be switched off

Suspend -> Off Always On All Mode -> Off

#### Video Off Method

This determines the manner in which the monitor is blanked.

V/H SYNC+Blank cause the system to turn off the vertical and horizontal

synchronization signals and writes blanks to the

screen.

Blank Screen This option only writes blanks to the screen.

DPMS Initial display power management signaling.

#### Modem Use IRQ

Name the interrupt request (IRQ) assigned to the modem (if any) on your system. Activity of the selected IRQ always awakens the system.

# Soft-Off By PWRBTN

The field defines the power-off mode when using an ATX power supply. The Instant-Off mode means powering off immediately when pressing the power button. In the Delay 4 Sec mode, the system powers off when the power button is pressed for more than four seconds or places the system in a very low-power-usage state, with only enough circuitry receiving power to detect power button activity or resume by ring activity when press for less than four seconds. The default is 'Instant-Off'.

#### State After Power Failure

This item allows you to select three status after the power failure. The choices are ON, OFF and Auto.

# Wake Up Events

Setting an event on each device listed to awaken the system from a soft off state.

Power Button

Wake Up on LAN

Wake Up on Modem

RTC Alarm Resume

# PnP/PCI Configuration

$\uparrow \downarrow \rightarrow \leftarrow : Move \ \, Enter: Select \, +/-/PU/PD: Value \ \, F10: Save \ \, ESC: Exit \ \, F1: General \ \, Help \ \, F5: Previous Values \ \, F6: Fail-SAfe Defaults \ \, F7: Optimized Defaults$

This section describes configuring the PCI bus system. PCI, or Personal Computer Interconnect, is a system which allows I/O devices to operate at speeds nearing the speed the CPU itself uses when communicating with its own special components.

#### PnP OS Installed

Select Yes if the system operating environment is Plug-and-Play aware (e.g., Windows 95).

# **Reset Configuration Data**

Normally, you leave this field Disabled. Select Enabled to reset ESCD (Extended System Configuration Date) when you exit Setup if you have installed a new add-on and the system reconfiguration has caused such a serious conflict that the operating system cannot boot.

#### Resource Controlled By

The Award Play and Play BIOS can automatically configure all the boot and Plug-and-Play compatible devices. If you select Auto, all the interrupt request (IRQ) and DMA assignment fields disappear, as the BIOS automatically assigns them.

#### **IRQ** Resources

When resources are controlled manually, assign each system interrupt as one of the following types, depending on the type of device using the interrupt:

Legacy ISA Devices compliant with the original PC/AT bus specification, requiring a specific interrupt (such as IRQ4 for serial port 1).

PCI/ISA PnP Device compliant with the Plug and Play standard, whether designed for PCI or ISA bus architecture.

#### **DMA** Resources

When resources are controlled manually, assign each system DMA channel as one of the following types, depending on the type of device using the DMA:

Legacy ISA Devices compliant with the original PC/AT bus specification, requiring a specific DMA channel.

PCI/ISA PnP Devices compliant with the Plug and Play standard, whether designed for PCI or ISA bus architecture.

#### PCI/VGA Palette Snoop

Normally this option is always Disabled! Nonstandard VGA display adapters such as overlay cards or MPEG video cards may not show colors properly. Setting Enabled should correct this problem. If this field set Enabled, any I/O access on the ISA bus to the VGA card's palette registers will be reflected on the PCI bus. This will allow overlay cards to adapt to the changing palette colors.

#### Assign IRQ For VGA

Many high-end graphics accelerator cards now require an IRQ to function properly. Disabling this feature with such cards will cause improper operation and/or poor performance. Thus, it's best to make sure you enable this feature if you are having problems with your graphics accelerator card. However, some low-end cards don't need an IRQ to run normally. Check your graphics card's documentation (manual). If it states that the card does not require an IRQ, then you can disable this feature to release an IRQ for other uses. When in doubt, it's best to leave it enabled unless you really need the IRQ.

#### Assian IRQ For USB

Windows 95 will automatically give an IRQ to the USB port even if there is no USB peripheral connected. Disabling this will free the IRQ.

# **PC Health Status**

# **Current CPU Temperature**

Show you the current CPU temperature

# **Current System Temperature**

Show you the current system temperature

# **Current CPUFAN Speed**

Show you the current CPUFAN operating speed

#### Vcore

Show you one type of CPU voltage

# +2.5, +3.3V, +5V, +12V

Show you the different voltage can be used for the system

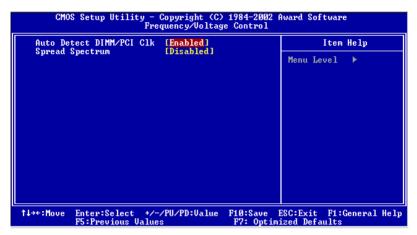

# Frequency/Voltage Control

This section describes Frequency and Voltage control for the system.

#### Auto Detect DIMM/PCI CLK

When enabled, this item will auto detect if the DIMM and PCI socket have devices and will send clock signal to DIMM and PCI devices. When disabled, it will send the clock signal to all DIMM and PCI socket.

# Spread Spectrum

This item allows you to enable/disable the spread spectrum modulate.

# POST Codes

The following codes are not displayed on the screen. They can only be viewed on the LED display of a so called POST card. The codes are listened in the same order as the according functions are executed at PC startup. If you have access to a POST Card reader, you can watch the system perform each test by the value that's displayed. If the system hangs (if there's a problem) the last value displayed will give you a good idea where and what went wrong, or what's bad on the system board.

| CODE | DESCRIPTION OF CHECK                                                                                                                                                                                                                 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CFh  | Test CMOS R/W functionality.                                                                                                                                                                                                         |

| C0h  | Early chipset initialization: -Disable shadow RAM -Disable L2 cache (socket 7 or below) -Program basic chipset registers                                                                                                             |

| C1h  | Detect memory -Auto-detection of DRAM size, type and ECCAuto-detection of L2 cache (socket 7 or below)                                                                                                                               |

| C3h  | Expand compressed BIOS code to DRAM                                                                                                                                                                                                  |

| C5h  | Call chipset hook to copy BIOS back to E000 & F000 shadow RAM.                                                                                                                                                                       |

| 0h1  | Expand the Xgroup codes locating in physical address 1000:0                                                                                                                                                                          |

| 02h  | Reserved                                                                                                                                                                                                                             |

| 03h  | Initial Superio_Early_Init switch.                                                                                                                                                                                                   |

| 04h  | Reserved                                                                                                                                                                                                                             |

| 05h  | Blank out screen     Clear CMOS error flag                                                                                                                                                                                           |

| 06h  | Reserved                                                                                                                                                                                                                             |

| 07h  | Clear 8042 interface     Initialize 8042 self-test                                                                                                                                                                                   |

| 08h  | <ol> <li>Test special keyboard controller for Winbond 977<br/>series Super I/O chips.</li> <li>Enable keyboard interface.</li> </ol>                                                                                                 |

| 09h  | Reserved                                                                                                                                                                                                                             |

| 0Ah  | <ol> <li>Disable PS/2 mouse interface (optional).</li> <li>Auto detect ports for keyboard &amp; mouse followed by a port &amp; interface swap (optional).</li> <li>Reset keyboard for Winbond 977 series Super I/O chips.</li> </ol> |

| 0Bh  | Reserved                                                                                                                                                                                                                             |

| 0Ch  | Reserved                                                                                                                                                                                                                             |

| 0Dh | Reserved                                                                                                                                                                                                 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0Eh | Test F000h segment shadow to see whether it is R/W-able or not. If test fails, keep beeping the speaker.                                                                                                 |

| 0Fh | Reserved                                                                                                                                                                                                 |

| 10h | Auto detect flash type to load appropriate flash R/W codes into the run time area in F000 for ESCD $\&$ DMI support.                                                                                     |

| 11h | Reserved                                                                                                                                                                                                 |

| 12h | Use walking 1's algorithm to check out interface in CMOS circuitry. Also set real-time clock power status, and then check for override.                                                                  |

| 13h | Reserved                                                                                                                                                                                                 |

| 14h | Program chipset default values into chipset. Chipset default values are MODBINable by OEM customers.                                                                                                     |